Buttons overview

As you can see from the screenshot, there are two buttons P0 and P1 which represents process P0 and P1. When you press P0 the process P0 will move and if you press P1, then process P1 will move.

Step 1

Here, if you press P0, then process P0 go will from queue to the entry section. When it enters the entry section, initially the value of the lock will be 0. When it enters into the critical section, a register will come into the picture. The value of the register will be 1.

Now in the entry section itself, the exchange of values between the register and the lock takes place.

Hence, the value of lock will become 1 and the value of register will become 0.

Step 2

Here once again if you press P0, then process P0 will go from entry section to the critical section. In critical section, only one process can occur at a time.

Step 3

Now if you press P1, then P1 will move from the queue to the entry section. Now again if you press P1 again, then there will be a problem as only one process can enter into the critical section.

Process P0 is already inside the critical section, so process P1 has to wait for P0 to finish the process.

As process P0 is already inside the critical section, the value of the register will become 1 and process P1 will go into the while loop and will never enter into the critical section.

The website will show an alert message that process P1 needs to wait for process P0 to leave the critical section.

Step 4

Now again when you press P0, then process P0 will go from critical section to the exit section.

In exit section the value of lock as well the value of the register will become 0. Again in the same time if you press P1 then again the value of lock will become 1.

Step 5

Now in the similar way if process P1 is in the critical section and process P0 is in entry section, then again if you press P0 the process P0 cannot enter into the critical section.

The value of the register will become 1 from zero and process P0 will enter into an infinite while loop refraining it from entering it into the critical section.

An alert message will come that process P0 needs to wait for process P1 to leave the critical section.

Step 6

Now consider a condition when process P0 and P1 are initially in the queue. Now process P0 will enter into the entry section. So the value of lock will be 1 and register will be 0.

Now at the same time, process P1 will come and it will enter into the entry section.

Now the value of register will become 1 hence neither process P0 nor process P1 can enter into the critical section which will lead to Deadlock.

Step 7

Now if any process goes from critical section to the exit section, then the value of lock and register will become 0, so that any other process can execute and utilize the critical section.

Analysis of Test And Set Lock

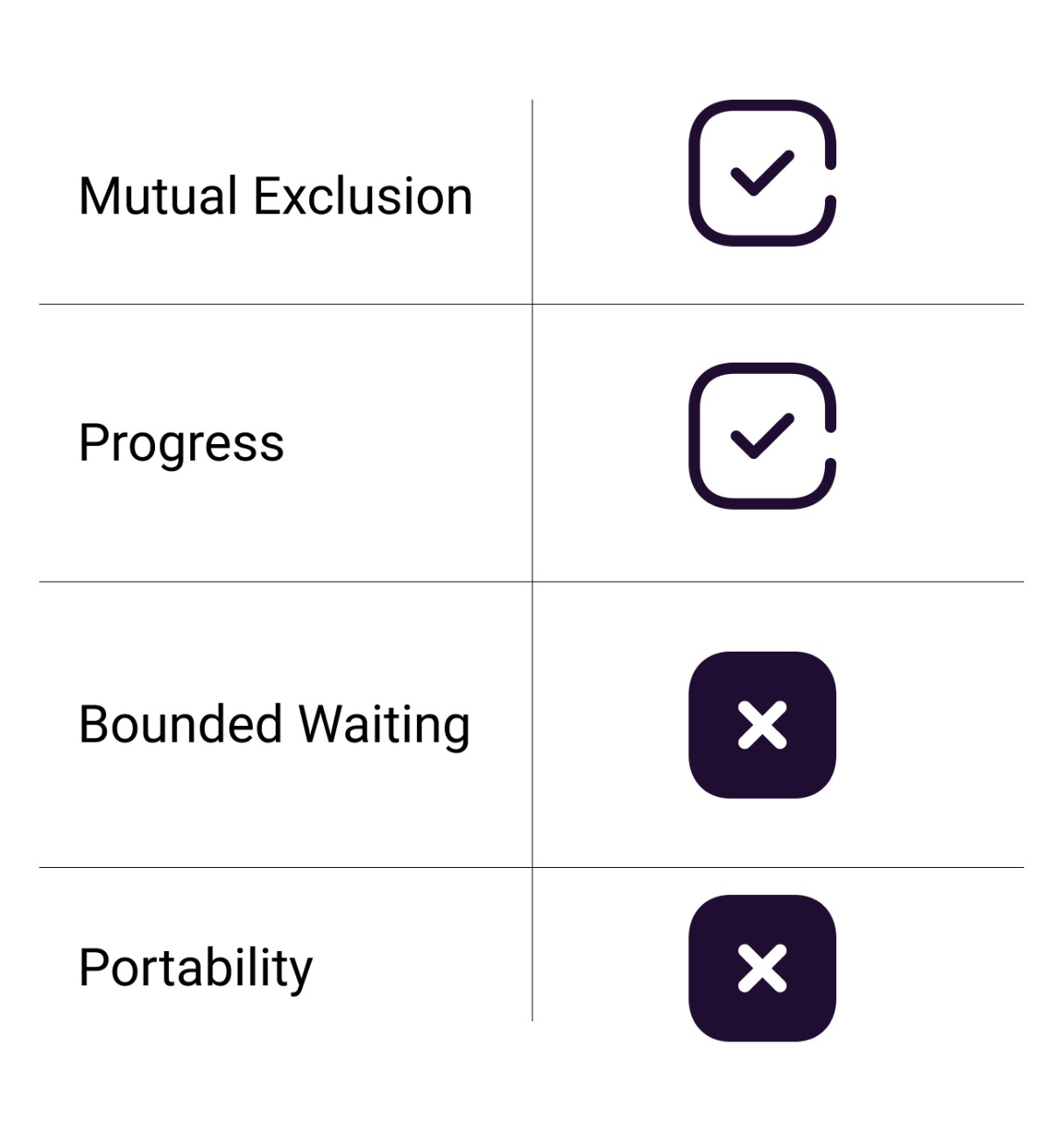

Mutual Exclusion

Mutual Exclusion is guaranteed in TSL mechanism since a process can never be preempted just before setting the lock variable. Only one process can see the lock variable as 0 at a particular time and that's why, the mutual exclusion is guaranteed.

Progress

According to the definition of the progress, a process which doesn't want to enter in the critical section should not stop other processes to get into it. In TSL mechanism, a process will execute the TSL instruction only when it wants to get into the critical section. The value of the lock will always be 0 if no process doesn't want to enter into the critical section hence the progress is always guaranteed in TSL.

Bounded Waiting

Bounded Waiting is not guaranteed in TSL. Some process might not get a chance for so long. We cannot predict for a process that it will definitely get a chance to enter in critical section after a certain time.

Architectural Neutrality

TSL doesn't provide Architectural Neutrality. It depends on the hardware platform. The TSL instruction is provided by the operating system. Some platforms might not provide that. Hence it is not Architectural natural.